A rail‐to‐rail low‐power latch comparator with time domain bulk‐tuned offset cancellation for low‐voltage applications - Shahpari - 2018 - International Journal of Circuit Theory and Applications - Wiley Online Library

A novel high-speed low-power dynamic comparator with complementary differential input in 65 nm CMOS technology - ScienceDirect

An efficient design of CMOS comparator and folded cascode op-amp circuits using particle swarm optimization with an aging leader and challengers algorithm | SpringerLink

PDF) Design & Simulation Results of a High Speed, Rail-to-Rail input CMOS comparator (500ps delay, 0-1.2V ICMR, UMC 130nm, 2mV resolution) | Pushpak Dagade - Academia.edu

An efficient design of CMOS comparator and folded cascode op-amp circuits using particle swarm optimization with an aging leader and challengers algorithm | SpringerLink

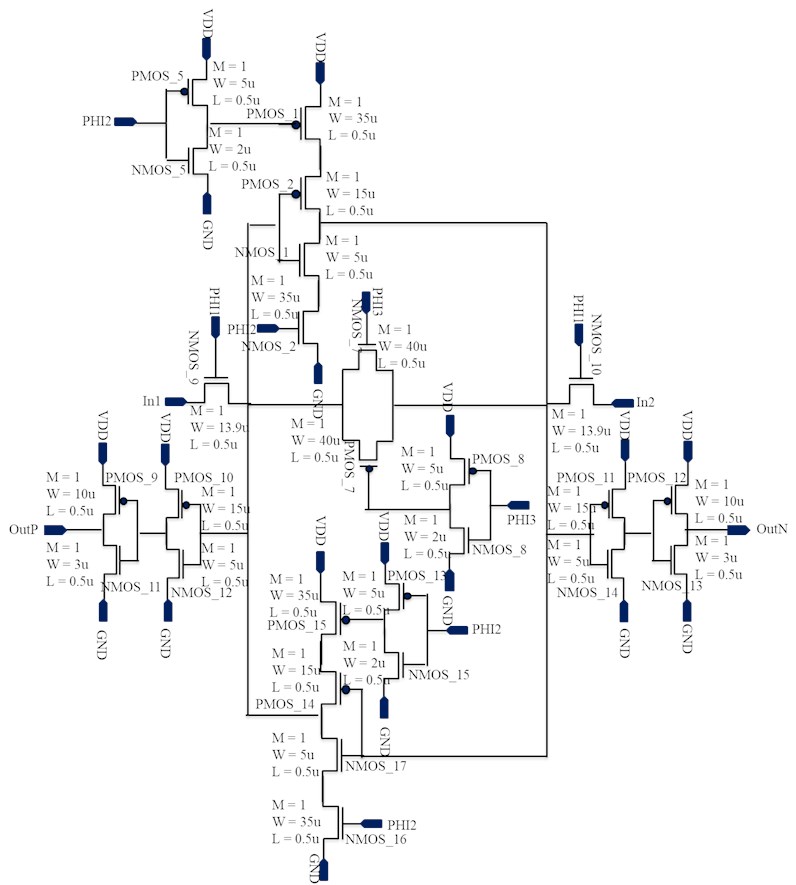

![CMOS Comparator with PMOS Input driver, De et al. [14] | Download Scientific Diagram CMOS Comparator with PMOS Input driver, De et al. [14] | Download Scientific Diagram](https://www.researchgate.net/publication/303814898/figure/fig3/AS:669145339269132@1536548089727/CMOS-Comparator-with-PMOS-Input-driver-De-et-al-14.jpg)